Poly-Poly(PIP)電容佈局

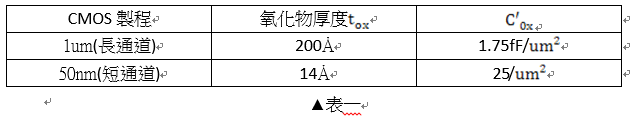

圖一、二展示了poly1與poly2組合成的PIP電容佈局,以及剖面圖。如圖所示,poly1的面積比poly2的面積還要大得多,是因為底板電容值可為所需電容值得20%,甚至更多都可以。兩個poly之間的間距大約與MOS電晶體裡的閘極氧化層厚度(Tox)一樣,其厚度如表一所示。

溫度係數

電容值會隨著溫度變化而變化。一階溫度係數為:

PIP電容的TCC典型值約為20ppm/C。

電容與溫度的函數關係:

寄生電容

在佈局時,所以的結構我們都必須考慮到寄生元件,如圖三所示,這是PIP電容所產生的寄生電容,其中最需注意的寄生電容是poly1到P基底的電容,這個電容的面積是最大的,也稱為底板寄生電容。